- 您现在的位置:买卖IC网 > Sheet目录1991 > CS43L22-CNZR (Cirrus Logic Inc)IC DAC W/HDPN & SPKR AMPS 40-QFN

26

DS792F2

CS43L22

Confidential Draft

3/4/10

4.5

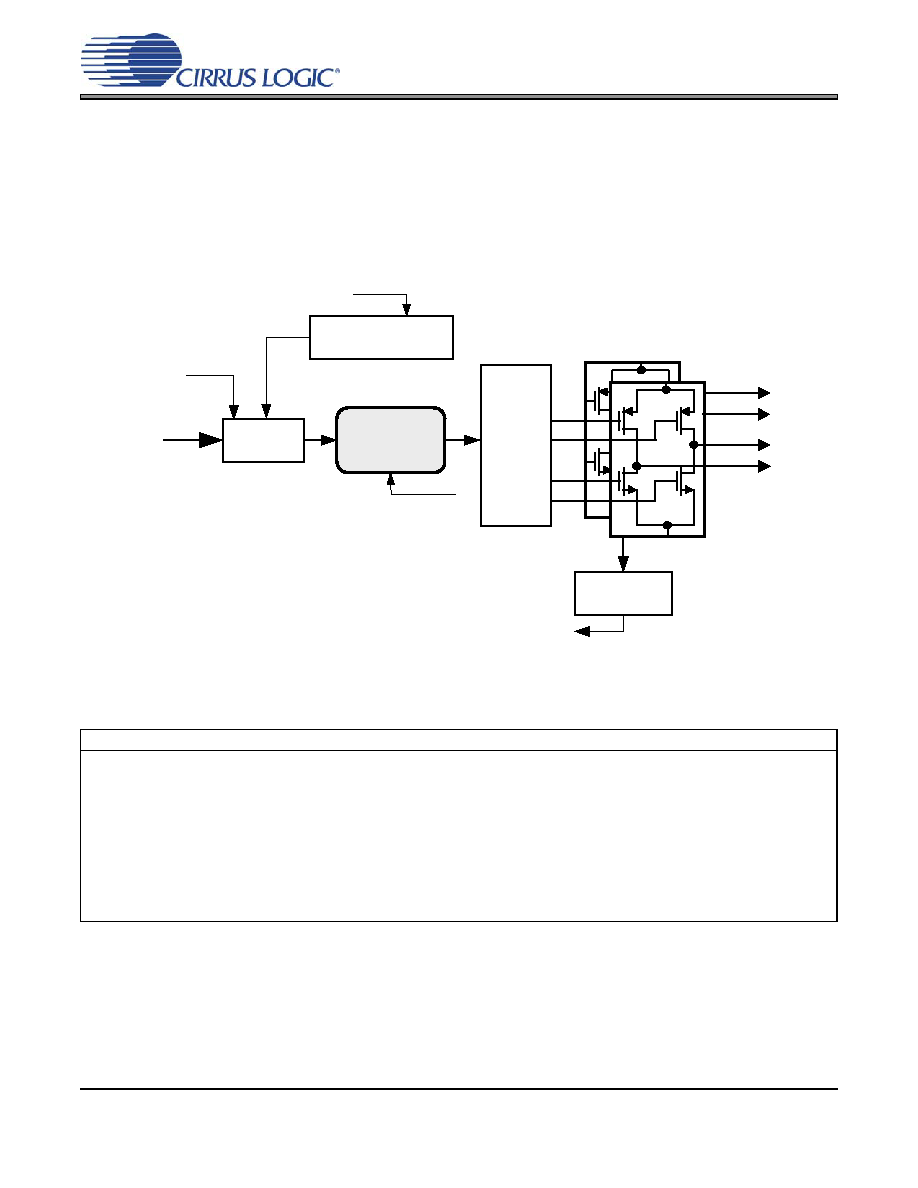

PWM Outputs

Note:

The PWM speaker amplifiers should not be used in the 384x MCLK modes (18.4320 and

16.9344 MHz).

Referenced Control

Register Location

PWM Control

SPKxMUTE .........................

MUTE50/50 .........................

SPKMONO ..........................

SPKxVOL[7:0] .....................

SPKSWAP...........................

SPKB=A ..............................

BATTCMP ...........................

VPREF[3:0] .........................

VPLVL[7:0] ..........................

PDN_SPKx[1:0]...................

SPKxSHRT..........................

VOL

PWM

Modulator

A

SPKAMUTE

SPKBMUTE

MUTE50/50

SPKMONO

SPKSWAP

SPKB=A

SPKAVOL[7:0]

SPKBVOL[7:0]

+0dB/-102dB

0.5dB steps

PDN_SPKA[1:0]

PDN_SPKB[1:0]

Short

Circuit

SPKASHRT

Battery

Compensation

BATTCMP

VPREF[3:0]

VPLVL[7:0]

SPKBSHRT

+

-

+

-

Gate

Drive

from DSP

Engine

Speaker

Outputs

B

Figure 10. PWM Output Stage

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CS4461-CZZR

IC ADC PSR FEEDBACK 24-TSSOP

CS5340-CZZ

IC ADC AUD 101DB 200KHZ 16-TSSOP

CS5340-DZZR

IC ADC AUD 101DB 200KHZ 16-TSSOP

CS5341-DZZ

IC ADC AUD 105DB 200KHZ 16-TSSOP

CS5342-CZZ

IC ADC AUD 105DB 200KHZ 16-TSSOP

CS5345-CQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5345-DQZ

IC ADC AUD 104DB 200KHZ 48-LQFP

CS5346-CQZR

IC ADC AUD 103DB 200KHZ 48-LQFP

相关代理商/技术参数

CS43L23-CWZR

功能描述:IC DAC W/HDPN & SPKR AMPS 40-QFN 制造商:cirrus logic inc. 系列:* 零件状态:Not For New Designs 标准包装:6,000

CS43L36-CNZ

功能描述:IC-LOWPOWERHIGHPERFORMANCE HEADP 制造商:cirrus logic inc. 系列:* 零件状态:在售 标准包装:490

CS43L41

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low Power 24-Bit, 96 kHz DAC with Volume Control

CS43L41-KZ

制造商:Rochester Electronics LLC 功能描述:- Bulk

CS43L42

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low Voltage,Stereo DAC With Headphone Amp

CS43L42-EP

制造商:Cirrus Logic 功能描述:

CS43L42-KZ

功能描述:数模转换器- DAC IC Low PWR Str DAC w/Hdphn & Line Amp RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube

CS43L42-KZR

功能描述:数模转换器- DAC IC Low PWR Str DAC w/Hdphn & Line Amp RoHS:否 制造商:Texas Instruments 转换器数量:1 DAC 输出端数量:1 转换速率:2 MSPs 分辨率:16 bit 接口类型:QSPI, SPI, Serial (3-Wire, Microwire) 稳定时间:1 us 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-14 封装:Tube